DESARROLLÓ E INNOVACIÓN TECNOLÓGICA Electrónica Autogenerado e Tranciscido Publicación autorizada

# Aplicación de dispositivo FPGA para la lectura rápida de un encoder absoluto de alta resolución

Brengi, D.; Trapanotto, A.; Farías, D.; Tropea S.; Gwirc, S.

INTI-Electrónica e Informática

#### Introducción

En este trabajo se presenta un sistema de adquisición para la lectura y almacenamiento de datos generados por un encoder absoluto de 14 bits utilizado como parte de un equipo desarrollado para una importante empresa nacional. El funcionamiento del equipo está basado en el análisis de la oscilación mecánica de un péndulo de torsión, de tal forma que cualquier variación en la masa y/o momento de inercia en el sistema se pueda medir y detectar sensando la posición del eje del péndulo.

### Metodología

Para sensar las oscilaciones en forma precisa y repetitiva se utiliza un encoder absoluto de 14 bits montado sobre el eje principal del sistema mecánico. Buscando mantener bajo el costo del sistema y permitir su utilización en cualquier computadora se decidió ingresar los datos por el puerto paralelo de una computadora tipo PC.

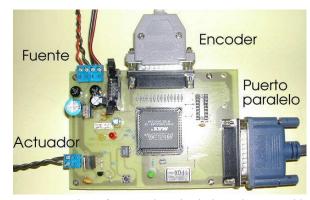

En lugar de utilizar el método tradicional de sensor y placa de adquisición para PC, se utiliza un dispositivo FPGA (Field Programmable Gate Array) como interfaz entre el sensor digital y el puerto paralelo de la computadora (ver Fig. 1). Esta solución permite implementar funciones complejas y de alta velocidad dentro de la propia interfaz entre sensor y PC. Por otra parte, la posibilidad de reconfigurar el comportamiento de la FPGA ofrece gran flexibilidad durante el desarrollo.

## Resultados

Para la implementación se utilizó un chip de Altera EPM7128 con 128 macroceldas empleando el 80% de las mismas. El comportamiento de la FPGA se describe en lenguaje VHDL (Very High Speed Integrated Circuit Hardware Description Language) para realizar las siguientes tareas:

- —Comunicarse con el puerto paralelo para la transferencia de los datos en modo EPP (Enhanced Parallel Port) cumpliendo el estándar IEEE1284.

- —Generación de la señal de sincronismo y de la base de tiempo (2 kHz) para el muestreo de los valores del encoder.

- —Conversión de código "gray" a binario para mejor interpretación desde la computadora.

- —Control de posición durante el impulso de excitación del péndulo. La FPGA controla que el desplazamiento inicial no supere el máximo establecido.

El programa de aplicación, desarrollado en lenguaje C, ejecuta en una computadora con sistema operativo Debian GNU/Linux y se encarga de leer los datos desde el puerto paralelo y guardarlos en disco para su posterior análisis.

#### **Conclusiones**

Se obtiene un sistema para la captura de datos desde un encoder absoluto de 14 bits, utilizando una FPGA como interfaz con el puerto paralelo de la computadora. Debido a la flexibilidad de la FPGA este tipo de interfase puede utilizarse en una gran variedad de aplicaciones similares con un mínimo de cambios en la programación del dispositivo.

Fig. 1: Circuito de interfase entre el encoder absoluto y el puerto paralelo de la computadora utilizando un chip FPGA.

Para mayor información contactarse con: Ing. Diego J. Brengi – <a href="mailto:brengi@inti.gov.ar">brengi@inti.gov.ar</a>