## **ELECTRÓNICA**

Desarrollo e Innovación

# Periférico para el cálculo de la varianza de una señal, descripción de hardware

Tropea, S. E.(i)

(i)INTI-Electrónica e Informática

## Introducción

En este trabajo presentamos el desarrollo de un periférico capaz de realizar el cálculo de la varianza de una señal analógica. El resultado del cálculo puede ser leído por un microcontrolador utilizando el estándar de interconexión WISHBONE<sup>[1]</sup>.

Este desarrollo fue realizado para uso no exclusivo de la empresa INVAP S.E.<sup>[2]</sup> y es utilizado en un sistema de seguridad y control de reactores nucleares, calificado para operar en ambiente espacial<sup>[3]</sup>.

El objetivo de este periférico es el de realizar un cálculo muy intensivo, y a altas velocidades, sin ocupar el tiempo de ejecución del microcontrolador principal. Dicho microcontrolador fue desarrollado por nuestro laboratorio<sup>[4] [5]</sup> y se trata de un microcontrolador compatible con el 16C84 de Microchip<sup>[6]</sup>. Dicho microcontrolador y sus periféricos debían poder sintetizarse para una *FPGA* de *Actel*<sup>[7]</sup> apta para aplicaciones aeroespaciales.

Como objetivo particular el cliente exigía que este periférico no ocupara más del 8% del área disponible en una *FPGA Spartan* II<sup>[8]</sup> 200 (XC2S200-6).

## Metodología

Las FPGAs son circuitos integrados reconfigurables y son los miembros más avanzados de la familia de circuitos lógicos programables. Una FPGA está compuesta por lógica combinacional, registros y mecanismos de interconexión para unir estos dos últimos. Todos estos recursos son reconfigurables de manera tal que se puede modificar el funcionamiento para que se ajuste a nuestras necesidades. Estos elementos se complementan con celdas de entrada y salida que permiten conectar nuestro circuito con el exterior.

Las *FPGAs* presentan una alternativa muy interesante cuando es necesario desarrollar un circuito integrado a medida. Los circuitos integrados realizados a medida poseen costos muy

elevados y sólo se justifican cuando el volumen de producción supera las decenas de miles. Esto es válido aún para los ASIC (Application Specific Integrated Circuit = Circuito Integrado de Aplicación Específica) que utilizan técnicas de fabricación de las conocidas como semi-custom en las que sólo una parte del proceso es específico del cliente y el resto son estándares. Cuando los volúmenes de producción son pequeños las *FPGAs* aparecen como una excelente alternativa. Las mismas no poseen grandes gastos iniciales o del tipo NRE (Non-Recurring Engineering) como en el caso de los ASICs. Por otra parte si se detectara un error en el diseño, o fuera necesario introducir otro tipo de cambio o mejora, las FPGAs pueden reconfigurarse sin ser necesario reemplazar el circuito integrado. Como contrapartida el costo por unidad de las FPGAs es superior, su velocidad es inferior y el consumo de energía es mayor cuando se las compara con los ASICs.

Dentro de una FPGA se puede incluir la funcionalidad de varios circuitos integrados. Esta funcionalidad puede ser desarrollada por el mismo equipo de trabajo o adquirida a través de un tercero. Debido a que estas funcionalidades son como componentes electrónicos, pero sin su parte física, se los suele llamar componentes virtuales. En la industria se los conoce como bloques de propiedad intelectual o IP cores.

El desarrollo de un *IP core* para una *FPGA* es muy similar al de un *ASIC*. En el caso de la *FPGA* el proceso se encuentra simplificado gracias a que nuestro circuito utilizará recursos ya probados y algo sobredimensionados. Este diseño se realiza utilizando lo que se conoce como lenguajes de descripción de hardware. Los mismos tienen cierto parecido con los lenguajes de programación de computadoras pero poseen diferencias conceptuales muy importantes. No se trata de programar un dispositivo sino de describir el comportamiento del mismo. Luego la descripción se convierte en una configuración para la *FPGA* utilizando herramientas de síntesis.

En nuestro desarrollo utilizamos el lenguaje de descripción de hardware VHDL (Very high speed integrated circuit Hardware Description Language = Lenguaje de Descripción de Hardware para Circuitos Integrados de Muy Alta Velocidad). Se trata de un lenguaje muy utilizado por agencias gubernamentales y en el área aeroespacial. El mismo fue originalmente desarrollado por el Departamento de Defensa Norteamericano y hoy se encuentra estandarizado por la IEEE (normas 1076, 1164 y accesorias).

El desarrollo fue verificado utilizando *FPGAs Spartan* II de *Xilinx*. Aún así el mismo fue realizado de manera tal que pudiera ser sintetizado con cualquier *FPGA*. Esto fue de vital importancia debido a que el cliente utiliza *FPGAs* de *Actel* tolerantes a rayos cósmicos, muy importante debido al hecho de que la aplicación final debía funcionar en el espacio.

Las herramientas de desarrollo utilizadas fueron las recomendadas por el proyecto FPGALibre<sup>[9][10][11]</sup> impulsado por nuestro laboratorio. Para este desarrollo se utilizaron estaciones de trabajo que corren Debian<sup>[12]</sup> GNU<sup>[13]</sup>/Linux.

El cálculo realizado consiste en el promedio del cuadrado de la suma entre una tensión de entrada y un offset determinado, ec.(1). Este cálculo coincide con la definición estadística de la varianza cuando el valor del offset es el valor medio de la señal, pero con signo opuesto. Dicho valor es configurable utilizando registros del periférico.

$$\frac{1}{N} \Box_{i=0}^{N-1} \Box V_i \Box V_{off} \dot{\Box}$$

(1)

De acuerdo con las especificaciones la tensión de entrada debía ser adquirida utilizando un conversor A/D (analógico/digital) a una frecuencia de aproximadamente 250.000 Hz, y que es configurable. El conversor A/D es de 16 bits con signo. El número de muestras a utilizar es configurable con un valor por defecto de 1024.

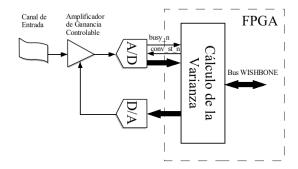

El periférico también debía incluir un registro para controlar la ganancia de un amplificador externo, previo al conversor A/D (ver Fig. 1).

Fig. 1: Diagrama en bloques de la interfaz entre la *FPGA* y los dispositivos externos.

La interfaz con el microcontrolador debía ser compatible con el bus WISHBONE y poseer un total de 12 registros. El resultado del cálculo es un valor representado en punto fijo con 32 bits de parte entera y 10 bits de parte decimal, es decir que posee 42 bits significativos (para el caso de 1024 muestras).

Se procedió a su implementación en *hardware* y a la creación de bancos de prueba que permitieran verificar el correcto funcionamiento del mismo.

### Resultados

Se obtuvo una descripción de un periférico capaz de calcular la varianza de una señal, escrito en *VHDL* estándar, y por lo tanto útil para ser utilizado con cualquier *FPGA*.

Este periférico es capaz de computar más de 250.000 productos, 500.000 sumas y 250 divisiones por segundo al mismo tiempo que controla las señales del conversor analógico digital. Todo esto se logra sin consumir recursos del microcontrolador principal, con una temporización perfecta y una resolución de 42 bits.

El área ocupada por el periférico fue de 159 *slices* lo que corresponde al 6,76 % de la *FPGA* antes mencionada.

No se utilizaron aproximaciones ni redondeos por lo que el resultado no contiene error alguno en sus 42 bits.

## Conclusiones

El periférico realizado logró cumplir con los objetivos de área ocupada, velocidad de cálculo y precisión de cálculo.

La utilización de *VHDL* estándar permitió que la descripción de hardware pudiera ser sintetizada para *FPGAs* de *Actel* aún cuando se desarrolló utilizando *FPGAs* de *Xilinx*.

La utilización de las herramientas propuestas por el proyecto FPGALibre mostró ser adecuada para

## este desarrollo.

#### Referencias

- [1] Silicore and OpenCores.Org, "WISHBONE System-on-Chip (SoC) Interconnection Architecture for Portable IP Cores", http://prdownloads.sourceforge.net/fpgalibre/wbspec\_b3-2.pdf?download

- [2] INVAP S. E., http://www.invap.net/

- [3] S. E. Tropea, R. M. Cibils, "Contador de pulsos nucleares para uso espacial", 6º Jornadas de Desarrollo e Innovación Tecnológica, Instituto Nacional de Tecnología Industrial, Argentina, 2007.

- [4] S. E. Tropea, J. P. D. Borgna, "Microcontrolador compatible con PIC16C84, bus Wishbone y video", *FPGA* Based Systems, ISBN 84-609-8998-4, 2006.

- [5] S. E. Tropea, "Microntrolador compatible con *PIC* 16C84, descripción de hardware", 6º Jornadas de Desarrollo e Innovación Tecnológica, Instituto Nacional de Tecnología Industrial, Argentina, 2007.

- [6] Microchip Technology Inc., http://www.microchip.com/

- [7] Actel Corporation, http://www.actel.com/

- [8] Xilinx Spartan II FPGA,

- http://www.xilinx.com/products/silicon\_solutions/fpgas/spartan\_series/spartan2\_fpgas/index.htm

- [9] S. E. Tropea, D. J. Brengi, J. P. D. Borgna, "FPGALibre: Herramientas de Software Libre para diseño con *FPGAs*", *FPGA* Based Systems, ISBN 84-609-8998-4, pp 173-180, 2006.

- [10] S. E. Tropea, D. J. Brengi, J. P. D. Borgna, S. N. Gwirc, "FPGALibre: Herramientas de Software Libre para diseño con *FPGAs*", 6º Jornadas de Desarrollo e Innovación Tecnológica, Instituto Nacional de Tecnología Industrial, Argentina, 2007.

- [11] Proyecto FPGA Libre, http://fpgalibre.sourceforge.net/

- [12] Debian project, http://www.debian.org/

- [13] GNU project, http://www.gnu.org/

Para mayor información contactarse con:

$Ing. \ Salvador \ E. \ Tropea \ - \ salvador@inti.gov.ar$

3