# Diseño de una Librería de Compuertas Estándares en Tecnología CMOS

Oroz De Gaetano Ariel, Alvarez Pablo Gabriel, Di Federico Martín, Julián Pedro DIEC, Universidad Nacional del Sur, Av. Alem 1253, Bahía Blanca, Buenos Aires, Argentina.

Resumen—El siguiente artículo muestra el diseño de una librería de compuertas lógicas implementadas en tecnología CMOS. Se describe brevemente sus topologías, el funcionamiento y se incluyen los esquemáticos de cada una de ellas así como también las máscaras que permiten su implementación en silicio. Entre las principales compuertas se encuentran la inversora, nand, nor, xor, compuerta de paso, etc.

### I. Introducción

$\bf R$  el diseño de circuitos integrados de aplicación específica (ASIC, por sus siglas en ingles *Aplication Specific Integrated Circuit*) es necesario contar con una librería de compuertas tanto para seguir un diseño tipo bottom up como top down [1]. Se comienza por la implementación de compuertas básicas que luego son combinadas para lograr compuertas o estructuras de complejidad mayor. En este trabajo se muestran los diseños de dichas compuertas elementales llevadas a cabo con la tecnología ON C5 de Mosis, un proceso n-well CMOS estándar de 0.5 μm, con tres capas de metal y dos de polysilicio. En esta tecnología se considera 5V como un valor lógico alto y 0V como uno bajo. El software utilizado para el diseño de los esquemáticos y máscaras es Tanner EDA.

Este trabajo está organizado de la siguiente manera: se presentan en la segunda sección aquellas compuertas elementales compuestas por pocos transistores y en la tercera sección las compuertas básicas construidas a partir de las elementales.

### II. COMPUERTAS ELEMENTALES

Esta sección incluye compuertas como la inversora, nand, nor, xor y compuerta de paso. Se muestra a continuación una tabla de verdad unificada indicando el comportamiento lógico de las mismas.

| A B | NAND | NOR | XOR |

|-----|------|-----|-----|

| 0.0 | 1    | 1   | 0   |

| 0.1 | 1    | 0   | 1   |

| 1 0 | 1    | 0   | 1   |

| 1 1 | 0    | 0   | 0   |

Cuadro I Tabla de verdad de la compuerta Nand.

# II-A. Inversor

La compuerta inversora es una de las celdas más simples en cuanto a cantidad de elementos y topología, constituyendo uno de los bloques elementales incluidos en otras compuertas básicas que se muestran posteriormente en este trabajo. Consiste en dos transistores, uno PMOS y otro NMOS, cuyos gates se encuentran conectados entre sí conformando el nodo de entrada tal como puede verse en la fig. 1. El drain del PMOS se conecta al drain del NMOS conformando el nodo de salida, los terminales bulk y source del transistor PMOS se conectan a la alimentación ( $V_{dd} = 5V$ ) mientras que los respectivos del NMOS se conectan a tierra.

Cuando en la entrada de la compuerta el nivel lógico es bajo  $V_{in} = 0V$ , el transistor NMOS se encuentra en corte debido a que su tensión de gate-source es nula  $(V_{gs} = 0V)$ y el nodo de salida se encuentra aislado del nodo de tierra. Por otro lado el transistor PMOS se encuentra encendido  $(V_{qs} = -V_{dd})$  operando en la región de triodo, produciendo que el nodo de salida quede directamente conectado a la alimentación resultando en una salida con nivel lógico alto. De manera análoga, cuando la entrada es un nivel lógico alto, es el transistor PMOS el que se encuentra en corte  $(V_{gs} = 0V)$ y el NMOS encendido y en la región de triodo ( $V_{qs} = V_{dd}$ ). Aquí el nodo de salida se encuentra conectado directamente a tierra y aislado del terminal de alimentación. De acuerdo a este análisis la función lógica determinada por la compuerta es  $OUT = \overline{IN}$ . En la fig. 2 se muestra la máscara del circuito, los terminales de gate se conectan entre sí con una linea de polysilicio, los terminales de drain de cada transistor se conectan entre si mediante una linea de metal uno. Las lineas de alimentación y tierra se colocan por debajo y encima respectivamente, fijando una distancia determinada (pitch) para todas las compuertas de esta librería.

Figura 1. Circuito esquemático del inversor.

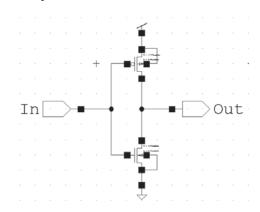

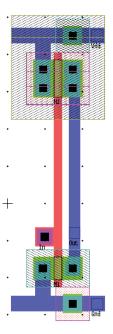

### II-B. Compuerta de paso

La compuerta de paso o de transmisión es el resultado de conectar un transistor PMOS y un NMOS en paralelo como

Figura 2. Máscara del inversor. Metal 1: azul; Polysilicio: rojo.

puede apreciarse en la fig. 3. Los respectivos terminales de gate de los transistores representan las entradas de habilitación  $(\overline{EN} \text{ y } EN)$  de la compuerta. Los terminales de drain y source pueden hacer las veces de entrada o de salida. De esta manera, conectando la salida de un inversor al terminal  $\overline{EN}$  del transistor PMOS, puede controlarse la habilitación de la compuerta con una sola señal lógica de habilitación permitiendo pasar un dato lógico del source al drain o viceversa. La principal ventaja de implementar la compuerta de transmisión con dos transistores en paralelo es que se asegura el paso de un dato lógico fuerte ya sea que se desee transmitir un 0 o un 1 lógico. La fig. 4 muestra la máscara de la compuerta.

Figura 3. Circuito esquemático de la compuerta de paso.

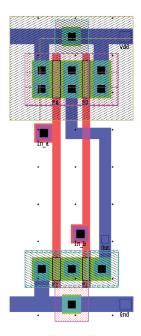

# II-C. Nand

Esta compuerta se compone de un total de cuatro transistores: dos PMOS conectados en paralelo entre la alimentación y la salida, y dos NMOS conectados en serie entre la salida y el terminal de tierra. Cada entrada se conecta al *gate* de un transistor PMOS y al de un NMOS, el esquema de conexión se muestra en la fig. 5. Dado que se cuenta con dos entradas, el valor lógico de la salida de la compuerta depende de cuatro posibles combinaciones entre las mismas como se explica a continuación.

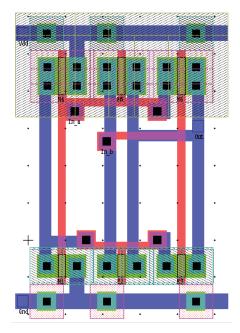

Figura 4. Máscara de la compuerta de paso.

Solo en caso que ambas entradas correspondan a un valor lógico alto, los transistores PMOS se encuentran en corte, aislando el nodo de salida de la alimentación mientras que los transistores NMOS se encuentran encendidos conectando la salida a tierra y produciendo así un nivel lógico bajo. En cualquier otra combinación de las entradas, alguno de los transistores PMOS conduce y alguno de los NMOS se encuentra en corte. De este modo la salida se ve desconectada de tierra y directamente conectada a la alimentación produciendo una salida de nivel lógico alto. En la fig. 6 se muestra la máscara de la compuerta.

Figura 5. Circuito esquemático de la compuerta Nand.

Figura 6. Máscara de la compuerta Nand.

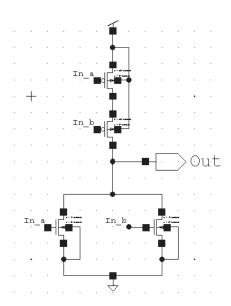

### II-D. Nor

Esta compuerta posee dos entradas y consiste en dos transistores PMOS conectados en serie entre la alimentación y la salida, y dos transistores NMOS conectados en paralelo entre la salida y tierra (fig. 7). Cuando ambas entradas corresponden a un valor lógico bajo, los transistores NMOS se encuentran en corte mientras que los PMOS estan encedidos, el nodo de salida está directamente conectado a la alimentación produciendo un nivel lógico alto. Para cualquier otra combinación de las entradas alguno de los transistores PMOS se encuentra en corte mientras que alguno de los NMOS encedido. Esto produce que la salida se encuentre aislada de la alimentación y conectada directo a tierra, produciendo una valor lógico alto en la salida. En la fig. 8 se muestra la máscara de la compuerta.

Figura 7. Circuito esquemático de la compuerta Nor.

Figura 8. Máscara de la compuerta Nor.

### II-E. Xor

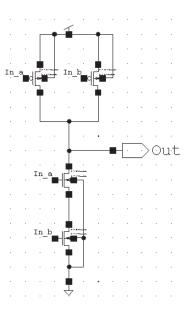

Esta compuerta posee dos entradas y una salida, su salida es un nivel lógico alto exclusivamente cuando una de las entradas se encuentra activa. Para esta implementación se utiliza un inversor, una compuerta de paso y dos transistores (uno PMOS y un NMOS) que se conectan como se muestra en el esquema de la fig. 9.

Para comprender el funcionamiento de la compuerta supongamos primero el caso en que la entrada A es de nivel lógico bajo. La salida del inversor será entonces un nivel alto produciendo que con A y  $\overline{A}$  en los terminales de habilitación, la compuerta de paso esté habilitada. Independientemente del valor de B los transistores mencionados anteriormente no conducirán y de este modo la entrada B es conducida por la compuerta de paso a la salida. En caso de que la entrada A sea un valor lógico alto, la salida del inversor será un nivel bajo, deshabilitando la compuerta de paso y produciendo que los transistores se comporten como un inversor. La salida será entonces la negación de la entrada B. La lógica anterior corrobora la tabla de verdad de la compuerta Xor. La fig. 10 muestra la máscara de la compuerta.

### III. COMPUERTAS BÁSICAS

Las compuertas presentadas en esta sección están constituidas por algunas de las que se introdujeron en la sección anterior, entre ellas se encuentran la compuerta inversora de tres estados, buffer de tres estados, latch y flip-flop D.

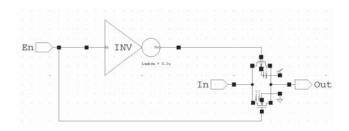

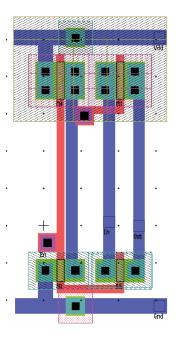

### III-A. Inversor de tres estados

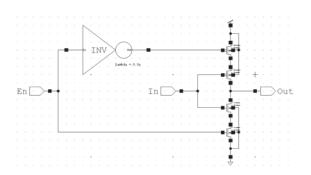

El inversor de tres estados se compone de una compuerta inversora a la cual se le integra una compuerta de paso como se ilustra en la fig. 11. El fin es obtener una compuerta que al ser habilitada se comporta como un inversor lógico, en caso

Figura 9. Circuito esquemático de la compuerta Xor.

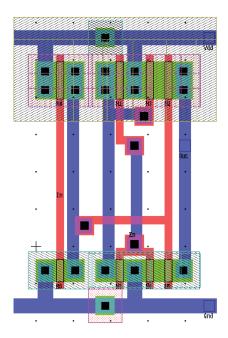

Figura 10. Máscara de la compuerta Xor.

contrario se encuentra en un estado de alta impedancia. En la máscara de esta compuerta (fig. 12) puede observarse como se aprovecha la disposición de los nodos de la topología para minimizar el largo de la celda al conectar de manera contigua todos los transistores PMOS y los NMOS.

Figura 11. Circuito esquemático de la compuerta inversora de tres estados.

Figura 12. Máscara de la compuerta inversora de tres estados.

### III-B. Buffer de tres estados

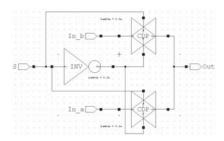

Un buffer de tres estados consiste en dos compuertas inversoras conectadas en cascada, con la particularidad que el inversor de la salida es de tres estados (fig. 13). De esta manera se tiene una compuerta que, al ser habilitada, pasa un dato lógico de la entrada sin modificar su valor. Su funcionalidad es útil en casos en los que se accede a un canal compartido de datos, se requiere regenerar una señal, aislar compuertas lógicas entre sí o aumentar la capacidad de carga de una compuerta. En la fig. 14 se muestra la máscara de la compuerta.

Figura 13. Circuito esquemático del buffer de tres estados.

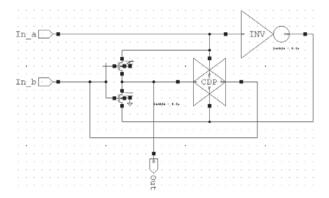

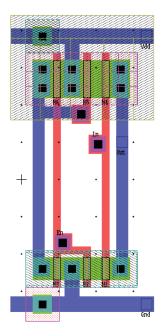

# III-C. Multiplexor de dos entradas

El multiplexor está conformado por dos compuertas de paso y un inversor, es decir que en total se trata de seis transistores (tres PMOS y tres NMOS). El caso del multiplexor de dos entradas, posee tres entradas y una salida. Dos de las entradas se conectan respectivamente a la entrada de cada compuerta de paso, mientras que la salidas de las mismas son conectadas entre si conformando el nodo de salida de la compuerta. La entrada restante denominada *select* (S) se utiliza para habilitar una compuerta de paso a la vez. De esta manera, y de acuerdo al esquema mostrado en la fig. 15, cuando la señal S corresponda a un nivel lógico bajo la compuerta de paso de la entrada A estará habilitada mientras que la de la entrada B

Figura 14. Máscara del buffer de tres estados.

estará deshabilitada. La salida entonces corresponderá al nivel lógico de la entrada A, en caso de que S sea un nivel alto sucederá lo opuesto y la salida corresponderá al nivel de la entrada B. La fig. 16 muestra la máscara de la compuerta.

Figura 15. Circuito esquemático del multiplexor de dos entradas.

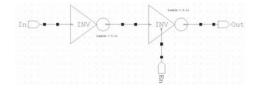

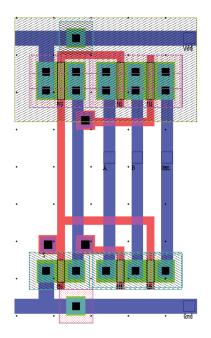

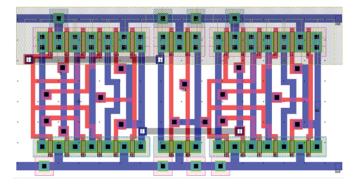

### III-D. Latch

De acuerdo con el esquemático de la fig. 17, el latch consta de dos compuertas de paso y cuatro inversores. El inversor que se encuentra conectado a la salida posee su entrada conectada a la salida de un multiplexor. Dependiendo la selección de este último el inversor pasa un dato, desde el inversor de la entrada a la salida (L=1), o se mantiene conduciendo el dato de la salida actual (L=0). En la fig. 18 se muestra la máscara de la compuerta.

## III-E. Flip-Flop D de flanco positivo

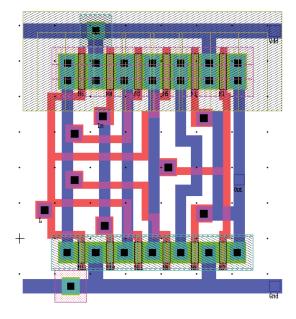

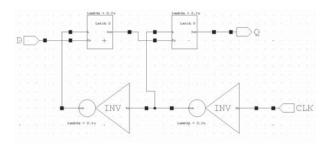

Para la implementación de esta compuerta se utilizan dos latches, donde la salida de uno de ellos se conecta a la entrada de datos del otro, y dos inversores utilizados para sus respectivas señales de reloj de manera que mientras uno es transparente el otro mantenga el dato y viceversa. Esta compuerta posee dos estados estables que la convierten en

Figura 16. Máscara del multiplexor de dos entradas.

Figura 17. Circuito esquemático del latch de flanco positivo.

Figura 18. Máscara del latch de flanco positivo.

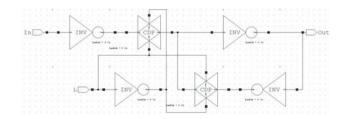

una unidad con capacidad de almacenar datos. El valor del estado de la salida (Q) en el esquema de la fig. 19 puede cambiarse aplicando señales a sus entradas, la de datos (D) y la de reloj (CLK). Particularmente el flip-flop D de flanco

| CLK             | D | $Q_{siguiente}$ |

|-----------------|---|-----------------|

| flanco positivo | 0 | 0               |

| flanco positivo | 1 | 1               |

| flanco negativo | X | Q               |

Cuadro II

TABLA DE VERDAD DEL FLIP-FLOP D.

ascendente permite el paso del dato lógico D a la salida Q ante la presencia de un flanco ascendente de reloj. Frente a cualquier otro evento, el dato se mantendrá a la salida sin variación siempre y cuando no se produzca un nuevo flanco ascendente de la señal de CLK.

En la máscara elaborada para la implementación de esta compuerta (fig. 20) puede observarse que se establecen dos conexiones utilizando metal dos debido a la complejidad de las compuertas que componen al flip-flop.

Figura 19. Circuito esquemático del flip-flop D.

Figura 20. Máscara del flip-flop D.

# IV. Conclusión

En este trabajo se presentó la librería de compuertas digitales para diseño de circuitos microelectrónicos. El incremento gradual en la complejidad de las compuertas mostradas remarca la importancia de un diseño de compuertas elementales que optimicen la utilización del área de silicio y a su vez exploten la utilización de conexiones en las primeras capas. Para cumplir estos requisitos puede ser necesario, como en el caso de las compuertas aquí presentadas, incrementar el ancho de las celdas.

Dado que la tecnología utilizada posee solo tres capas de metal, se prioriza en todas las compuertas la utilización de polysilicio y metal uno para establecer las conexiones. De esta forma se obtiene mayor grado de libertad a la hora de realizar

el conexionado de las compuertas en niveles superiores, donde metal dos y tres se encuentran disponibles para ser utilizados.

### REFERENCIAS

- N. Weste and K. Eshraghian, Principles Of CMOS VLSI Design, A Systems Perspective, 2nd ed. Addison-Wesley, 1993.

- [2] T. Schubert and E. Kim, Active and Nonlinear Electronics. John Wiley and Sons, 1996.

- [3] J. M. Rabaey, A. Chandrakasan and B. Nikolic, *Digital Integrated Circuits A design Perspective*. Pearson, 2004.