# Análisis del Comportamiento de un Inversor de Tres Estados

Alvarez Pablo Gabriel, Oroz De Gaetano Ariel, Di Federico Martín, Julián Pedro DIEC, Universidad Nacional del Sur, Av. Alem 1253, Bahía Blanca, Buenos Aires, Argentina.

Resumen—En este trabajo se analiza el comportamiento de una compuerta inversora de tres estados considerando la influencia de las capacidades parásitas de los transistores. Para esto se analizan los niveles de tensión de la señal de salida sin carga teniendo en cuenta diferentes combinaciones de la señal de entrada y de habilitación .

## I. Introducción

L inversor lógico de tres estados es una compuerta compuesta por cuatro transistores (un par PMOS y otro par NMOS) dos de los cuales se utilizan como etapa inversora y los restantes conforman una compuerta de paso. La elección del par de transistores que compone al inversor y el de la compuerta de paso depende del diseño, resultando ambas en configuraciones lógicamente iguales. Si se analiza la salida ante distintas variaciones de la entrada y la señal de habilitación, se observan diferencias entre los niveles de tensión que se deben a las cargas retenidas en las capacidades parásitas de los transistores. Se presentan en este trabajo dos esquemas de conexión y en cada uno se analizan los fenómenos producidos a la salida ante cada combinación de las entradas.

La compuerta se implementa utilizando lógica CMOS complementaria, el diseño y la construcción de las máscaras se realizaron con el programa Tanner EDA. La tecnología utilizada fue ON C5N de Mosis y ocupa un tamaño de 35  $\mu \rm m$  x 70  $\mu \rm m$ . Se considera como valor lógico alto una tensión de 5 V y como valor lógico bajo 0V.

#### II. ANÁLISIS

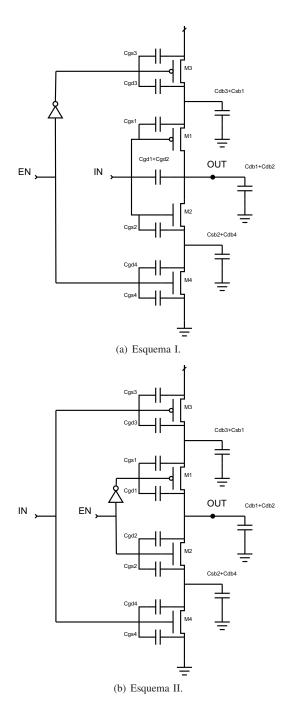

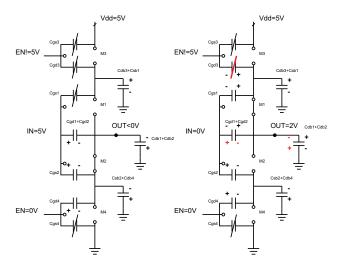

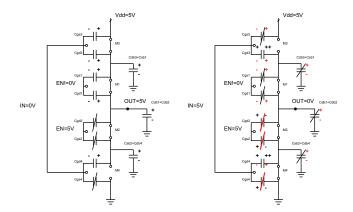

En los esquemáticos mostrados en la fig. 1 pueden apreciarse las dos formas de conectar las entradas para conformar la compuerta inversora de tres estados junto con todas las capacidades parásitas involucradas. En el caso de la fig. 1(a) denominado Esquema I, la señal de entrada de datos (IN) se conecta al nodo formado por los gates de los transistores  $M_1$  y  $M_2$  mientras que la señal de habilitación (EN) es conectada directamente al gate del transistor  $M_4$  y su versión negada al del  $M_3$ . De este modo  $M_1$  y  $M_2$  componen al inversor mientras que  $M_3$  y  $M_4$  la compuerta de paso. La fig. 1(b) muestra la situación inversa donde el inversor lo conforman  $M_3$  y  $M_4$ , y la compuerta de paso los transistores  $M_1$  y  $M_2$ , se denomina Esquema II a esta configuración.

# II-A. Esquema I

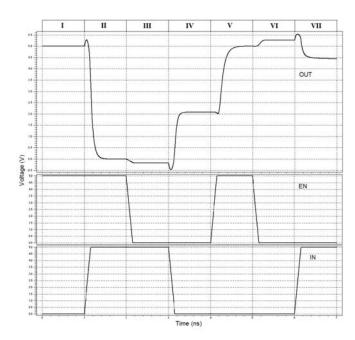

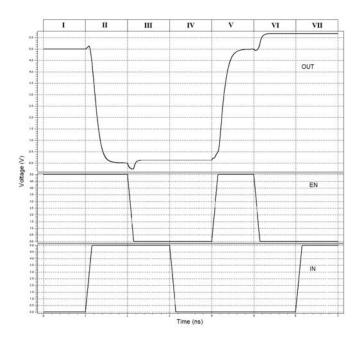

Las combinaciones de las entradas IN y EN junto con la salida del inversor en el Esquema I se muestran en la fig. 2.

Figura 1. Esquemas de conexión del inversor de tres estados.

Figura 2. Salida del inversor, señal de habilitación EN y señal de datos IN.

Se separa cada par de entradas y sus variaciones en estados numerados del I al VII y se explica el fenómeno resultante en la tensión de salida en las subsecciones siguientes.

II-AI. Transición del Estado I al Estado II: En esta transición la señal de habilitación EN se mantiene en nivel lógico alto mientras que la de entrada pasa de un nivel lógico bajo, en el Estado I, al nivel lógico alto en el Estado II. Se observa en la tensión de salida que se produce un sobrepico antes que la tensión cambie al valor lógico bajo. Esto es producto de la capacidad parásita resultante  $C_{gd1} + C_{gd2}$ , que se encuentra cargada de manera que el nodo de mayor potencial se encuentra en la salida y cuando la entrada cambia al valor alto, el nodo de bajo potencial del capacitor tiende a aumentar su tensión y por ende su nodo de mayor potencial también lo hace (de allí el sobrepico), un instante después conduce el transistor  $M_2$  y la capacidad descarga a tierra.

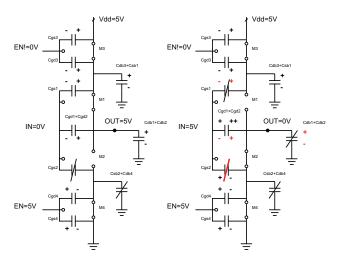

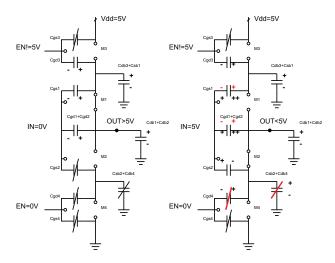

En la fig. 3 se muestran las polaridades de los capacitores en cada estado. Los capacitores atravesados por una línea son los que no se encuentran cargados o no varían su carga. En rojo se indican las polaridades tal como estaban en su estado previo.

II-A2. Transición del Estado II al Estado III: Durante esta transición la entrada de datos no modifica su valor lógico alto (IN=1) mientras que la habilitación cambia del valor alto al bajo, deshabilitando la compuerta de paso. La salida cambia a un nivel de alta impedancia donde la tensión es menor a 0V en el Estado III. Esto es consecuencia de la capacidad  $C_{gd4}$ , cargada durante el Estado II como muestra la fig. 4, que al cortarse  $M_4$   $(EN=1\rightarrow 0)$  no posee medios por donde descargarse. De esta manera el nodo de salida es disminuido a un potencial inferior al de tierra.

Figura 3. Variación en las cargas durante la transición del Estado I al Estado II.  $EN=1,\ IN=0 \to IN=1.$

Figura 4. Variación en las cargas durante la transición del Estado II al Estado III.  $IN=1,\,EN=1\to EN=0.$

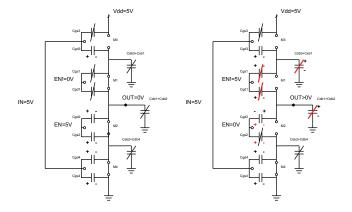

II-A3. Transición del Estado III al Estado IV: Esta es una de las transiciones más particulares de esta configuración dado que la compuerta permanece siempre deshabilitada (EN=0) y es la entrada la que cambia del valor lógico alto al bajo. Inmediatamente después de la transición se produce un sobrepico (negativo) que responde al mismo efecto explicado en el primer caso, esta vez con la polaridad invertida en  $C_{gd1}+C_{gd2}$ . Luego la salida se eleva en tensión hasta alcanzar un punto aproximadamente medio entre la alimentación y tierra. La causa de este comportamiento es que la capacidad resultante  $C_{db3}+C_{sb1}$ , que se encuentra cargada en el Estado III como muestra la fig. 5, distribuye su carga con la capacidad  $C_{db1}+C_{db2}$  al conducir  $M_1$ .

$\it II-A4$ . Transición del Estado V al Estado VI: En este análisis la entrada es un nivel lógico bajo que no varía ( $\it IN=0$ ) mientras que la habilitación cambia de un nivel alto a uno bajo, deshabilitando la compuerta. El fenómeno observable a la salida es que la tensión de la misma supera al valor de la alimentación. Durante el Estado V la salida se

Figura 5. Variación en las cargas durante la transición del Estado III al Estado IV.  $EN=0,\ IN=1 \to IN=0.$

Figura 6. Variación en las cargas durante la transición del Estado V al Estado VI.  $IN=0,\ EN=1 \to EN=0.$

encuentra en un nivel alto y la capacidad parásita  $C_{gd3}$  se encuentra cargada con polaridad como es mostrado en la fig. 6. Al producirse la transición en la habilitación  $(EN=1\rightarrow 0)$ ,  $C_{gd3}$  retiene su carga ya que no posee medios por donde descargarse y al encontrarse conectado a la salida, por medio de  $M_1$  que ahora conduce, eleva la tensión del nodo de salida.

$\it II-A5$ . Transición del Estado VI al Estado VII: En la última transición analizada la señal de habilitación se encuentra en nivel bajo sin variación ( $\it EN=0$ ) y es la entrada la que cambia de nivel bajo a alto. La compuerta se mantiene en alta impedancia durante la transición, se observa que la salida posee una tensión mayor a la alimentación en el Estado VI y luego en el estado siguiente siguiente el valor es algo inferior a la misma. Nuevamente ocurre un sobrepico en el primer instante de la transición, bajo la influencia ya mencionada de la capacidad  $\it C_{gd1} + \it C_{gd2}$ . El valor de tensión de la salida es causado por la carga acumulada en la capacidad  $\it C_{gs2}$  cuando la entrada cambia al valor lógico alto (fig. 7). Dado que el nodo de mayor potencial de la capacidad se encuentra del lado de

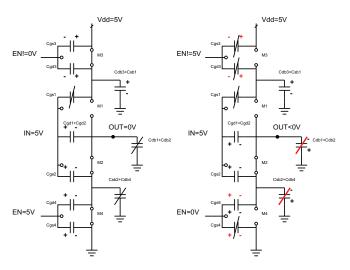

Figura 7. Variación en las cargas durante la transición del Estado VI al Estado VII.  $EN=0,\ IN=0 \to IN=1.$

Figura 8. Salida del inversor, señal de habilitación EN y señal de datos IN.

la entrada, y no se pierde carga, la salida se mantiene a un potencial menor a 5V.

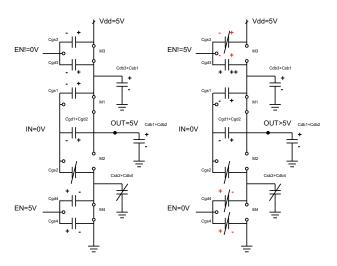

## II-B. Esquema II

De manera análoga se analizan las combinaciones de las entradas IN y EN junto con la salida del inversor en el Esquema II, se muestran en la fig. 8 los resultados de la simulación. Se separa cada par de entradas y sus variaciones en estados numerados del I al VII y se explica el fenómeno resultante en la tensión de salida en las subsecciones siguientes.

$\it II-B1$ .  $\it Transición del Estado I al Estado II$ : El efecto producido en esta transición es nuevamente un sobrepico, causado por el mismo efecto explicado en la Sección II-A1, aquí la compuerta de paso permanece habilitada ( $\it EN=1$ )

Figura 9. Variación en las cargas durante la transición del Estado I al Estado II.  $EN=1,\ IN=0 \to IN=1.$

Figura 10. Variación en las cargas durante la transición del Estado II al Estado III.  $IN=1,\,EN=1\to EN=0.$

mientras que la salida cambia de un valor lógico bajo al alto. La capacidad parásita que en este caso se encuentra cargada en el Estado I es  $C_{gd4}$ , en la fig. 9 se muestra la variación de carga en todas las capcaidades parásitas.

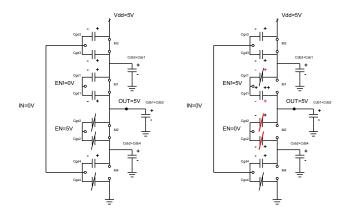

II-B2. Transición del Estado II al Estado III: En esta transición se deshabilita la compuerta de paso  $(EN=1 \rightarrow 0)$  mientras la señal de entrada permanece en nivel lógico alto. Se observa en primera instancia un sobrepico negativo como consecuencia que la capacidad  $C_{gd2}$  posee una polaridad como se muestra en la fig. 10 y al producirse la transición se decrementa el potencial en su nodo positivamente cargado. Disminuye entonces momentáneamente el potencial de la salida y  $C_{gd2}$  invierte su polaridad. La entrada  $\overline{EN}$ , ahora en estado alto, carga las capacidades  $C_{gd1}$  y  $C_{db1}+C_{db2}$  resultando la salida en una tensión levemente por encima de 0V.

II-B3. Transición del Estado III al Estado IV: En forma contrapuesta al caso anterior, en esta transición se deshabilita la compuerta mientras la entrada es un nivel lógico bajo (IN = 0). Durante el Estado III la salida está en nivel alto y las capacidades  $C_{gd1}$  y  $C_{db1}+C_{db2}$  se encuentran cargadas como indica la fig. 11. Luego de la transición, la salida queda aislada de tierra y la alimentación, la entrada  $\overline{EN}$  pasa a un nivel alto elevando consigo el potencial del nodo de  $C_{gd1}$  conectado a

Figura 11. Variación en las cargas durante la transición del Estado III al Estado IV.  $IN=0,\ EN=1 \to EN=0.$

esta. Dado que  $C_{gd1}$  no posee medios por donde descargarse, su nodo conectado a la salida también aumenta su potencial elevando la tensión de salida a un valor levemente mayor a 5V.

### III. CONCLUSIÓN

Se analizó en este trabajo los dos esquemas de conexión presentados y el efecto de la variación de sus entradas reflejado en el valor de tensión de la salida, considerando todas las capacidades parásitas presentes cuando se utiliza tecnología CMOS. Es necesario observar también que todos los análisis de los inversores son llevados a cabo sin carga, la misma podría influir significativamente sobre los niveles de tensión a la salida simulados y en la velocidad con que los cambios se presentan en ella.

## REFERENCIAS

- [1] N. Weste and K. Eshraghian, *Principles Of CMOS VLSI Design, A Systems Perspective*, 2nd ed. Addison-Wesley, 1993.

- [2] T. Schubert and E. Kim, Active and Nonlinear Electronics. John Wiley and Sons, 1996.

- [3] J. M. Rabaey, A. Chandrakasan and B. Nikolic, *Digital Integrated Circuits A design Perspective*. Pearson, 2004.